台积电首次公开2nm!性能提升15%、功耗降低35%

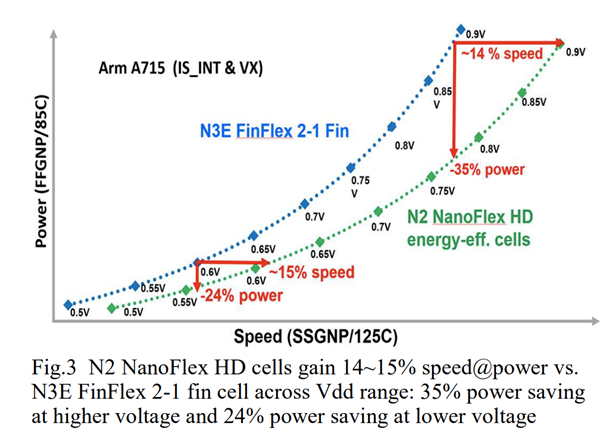

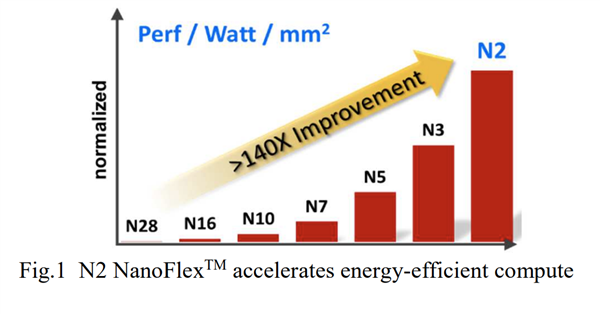

快科技12月15日消息,IEDM 2024大会上,台积电首次披露了N2 2nm工艺的关键技术细节和性能指标:对比3nm,晶体管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。

台积电首次公开2nm!性能提升15%、功耗降低35%

台积电2nm首次引入全环绕栅极(GAA)纳米片晶体管,有助于调整通道宽度,平衡性能与能效。新工艺还增加了NanoFlex DTCO(设计技术联合优化),可以开发面积最小化、能效增强的更矮单元,或者性能最大化的更高单元。此外还有第三代偶极子集成,包括N型、P型,从而支持六个电压阈值档(6-Vt),范围200mV。

台积电首次公开2nm!性能提升15%、功耗降低35%

通过种种改进,N型、P型纳米片晶体管的I/CV速度分别提升了70%、110%。

对比传统的FinFET晶体管,新工艺的纳米片晶体管可以在0.5-0.6V的低电压下,获得显著的能效提升,可以将频率提升大约20%,待机功耗降低大约75%。

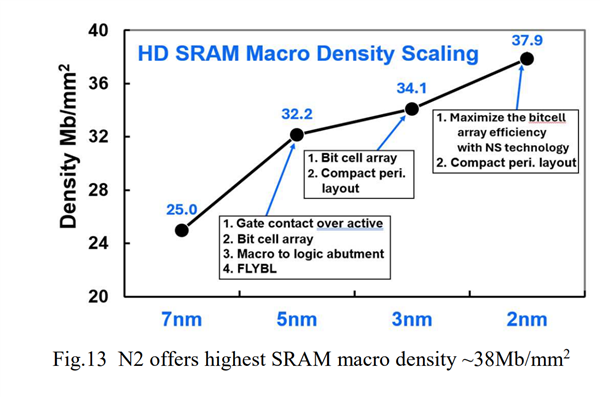

SRAM密度也达到了创纪录的新高,每平方毫米约38Mb。

台积电首次公开2nm!性能提升15%、功耗降低35%

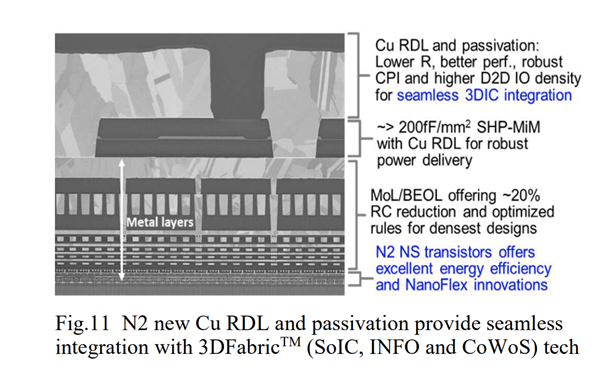

此外,台积电2nm还应用了全新的MOL中段工艺、BEOL后段工艺,电阻降低20%,能效更高。

值得一提的是,第一层金属层(M1)现在只需一步蚀刻(1P1E)、一次EVU曝光即可完成,大大降低了复杂度、光罩数量。

针对高性能计算应用,台积电2nm还引入了超高性能的SHP-MiM电容,容量大约每平方毫米200fF,可以获得更高的运行频率。

台积电首次公开2nm!性能提升15%、功耗降低35%

按照台积电的说法,28nm工艺以来,历经六代工艺改进,单位面积的能效比已经提升了超过140倍!

台积电首次公开2nm!性能提升15%、功耗降低35%

【本文结束】出处:快科技

版权声明

本站所有文章来源于本站原创或网络,如有侵权请联系删除。文章观点并不代表本站观点,请网友自行判断,如涉及投资、理财请谨慎应对!

德阳吧

德阳吧

发表评论:

◎欢迎参与讨论,请在这里发表您的看法、交流您的观点。