三代锐龙CPU I/O裸片彩色透视图公布:“五脏六腑”毕现

基于7nm Zen2架构的AMD产品家族的布局接近圆满,它们在市场上也取得不俗反响。

经发烧友挖掘,锐龙CPU内核的更多技术细节曝光在我们面前。

基于Fitzchens Fitz的裸片透视,工程师Nemez用彩图的形式将“Matisse(对应锐龙3000 CPU)”和“Rome(对应第二代EPYC霄龙)”中IO芯片的“五脏六腑”给标记了出来。

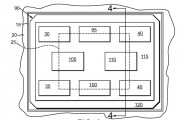

图为Matisse

这里简单解释下,锐龙3000 CPU、EPYC 2霄龙采取的都是CCD+I/O Die的封装方式,一个CCD对应8核Zen2,而I/O裸片采用14nm工艺打造,CCD的结构,AMD官方有公布,这里绘制的是I/O Die“彩超”。

图为Rome

以“Matisse”为例,I/O裸片中拥有两个x16 SerDes主控(可同时管理PCIe、SATA、USB 3等接口)、一个I/O根核心、两个x16 SerDes物理层等。

对比“Rome”,x16 SerDes主控多达8个,而三代锐龙线程撕裂者(Castle Peak)则屏蔽了其中4个,对于消费者来说,这也就是三代撕裂者限制为四通道内存的根本原因。

版权声明

本站所有文章来源于本站原创或网络,如有侵权请联系删除。文章观点并不代表本站观点,请网友自行判断,如涉及投资、理财请谨慎应对!

德阳吧

德阳吧

发表评论:

◎欢迎参与讨论,请在这里发表您的看法、交流您的观点。